# **Andreas Olenyi SOC-COE Application Consultant** • 27 March, 2001 Testing High-Speed HyperTransport Interfaces on Agilent 93000 SOC **Agilent Technologies**

### Content

- HyperTransport Overview

- HyperTransport Tests & Challenges

- High-Speed Source Synchronous Test

- Summary and Q&A

# HyperTransport Technology Overview

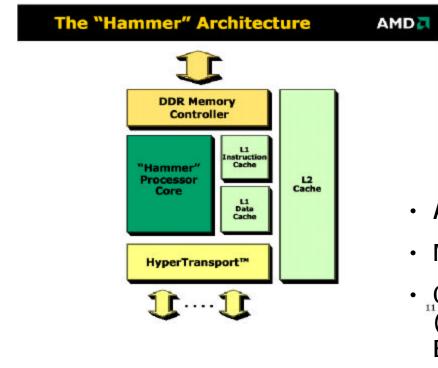

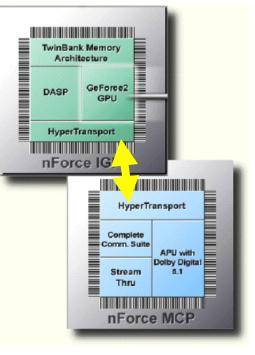

- Originally, HyperTransport was introduced by AMD

- Designed as high bandwidth solution for their next generation of Microprocessors.

Agilent Restricted

- A HyperTransport consortium was founded

- Meanwhile, many companies has joined

- Companies from different market segments (Transmeta, SUN, Cisco, PMC-Sierra, Broadcom)

Agilent Technologies

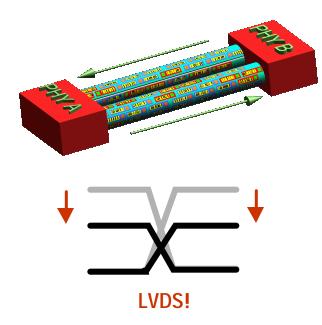

# What is HyperTransport?

- Scaleable I/O bus for high-speed operation

- Bus Width: 2, 4, 8, 16, 32

- Speed: 400Mbit ... 1.6 Gbit

- Designed for chip-to-chip link ('in the box')

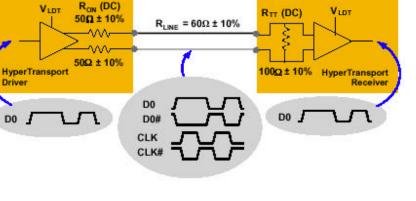

- Differential, LVDS type signaling

- Device Swing: Typ: 600 mV

- Common Mode voltage: Typ: 600 mV

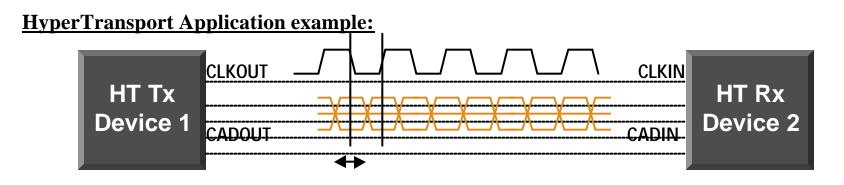

- Unidirectional bus (dedicated TX and RX lines)

- 100 Ohm Cross Termination

- 50 Ohm Driver Output Impedance

# List of Different HyperTransport Parameters

|            | PARAMETER   | DESCRIPTION                   | TESTED<br>with<br>93K/P800 | TESTED<br>with<br>NP1700 |              |

|------------|-------------|-------------------------------|----------------------------|--------------------------|--------------|

| Level:     | Vod         | Differential Output Voltage   | YES                        | YES                      |              |

|            | Vocm        | Output common-mode voltage    | YES                        | YES                      |              |

|            | Vid         | Differential Input Voltage    | YES                        | YES                      |              |

|            | Vicm        | Input common-mode voltage     | YES                        | YES                      |              |

| Impedance: | Rtt         | Differential Input Impedance  | YES                        | YES                      |              |

|            | Ron         | Driver Output Impedance       | YES                        | YES                      |              |

|            |             |                               |                            |                          | New Tester   |

| Timing:    | Tbit        | Bit Time 400 Mbps             | YES                        | YES                      | Capabilities |

| 5          |             | 800 Mbps                      | YES                        | YES 🖌                    |              |

|            |             | 1.6 Gbps                      | -                          | YES                      |              |

|            | Tcadv       | Transmitter output Clock/Data | YES                        | YES                      |              |

|            |             | skew                          | YES                        | YES                      |              |

|            | Tsu         | Receiver input setup time     | YES                        | YES                      |              |

|            | Tdh         | Receiver input hold time      | YES                        | YES                      |              |

|            | TpllIterror | PLL long term phase error     | -                          | YES                      |              |

|            | :           | :                             |                            |                          |              |

### HyperTransport Test Challenges

10 June, 2002 Testing High-Speed Interfaces

Agilent Restricted

- High Speed Data Rates up to 1.6 Gbit/s require Highest Speed and Accuracy

- Low Swing Differential Signals (DC/AC measurements)

- Debug & Characterize your High Speed Interface to bring your Device fast into production

- Source Synchronous bus interface

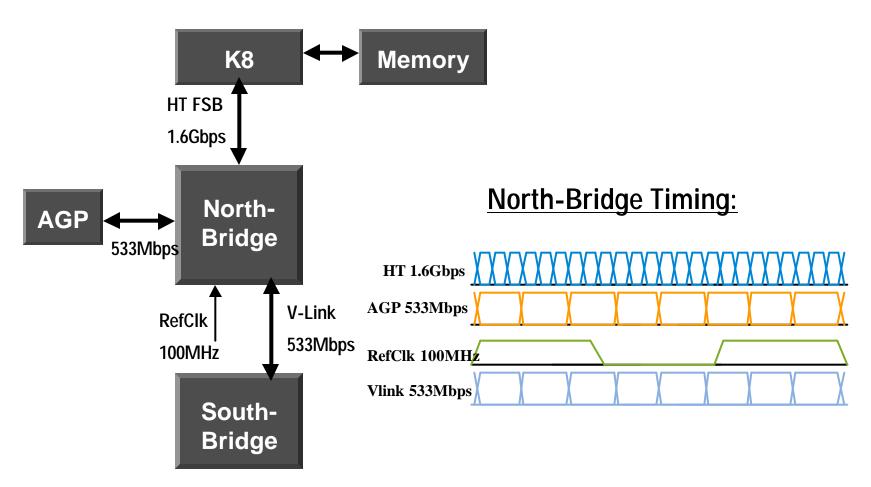

### **Application Example: North-Bridge Chip**

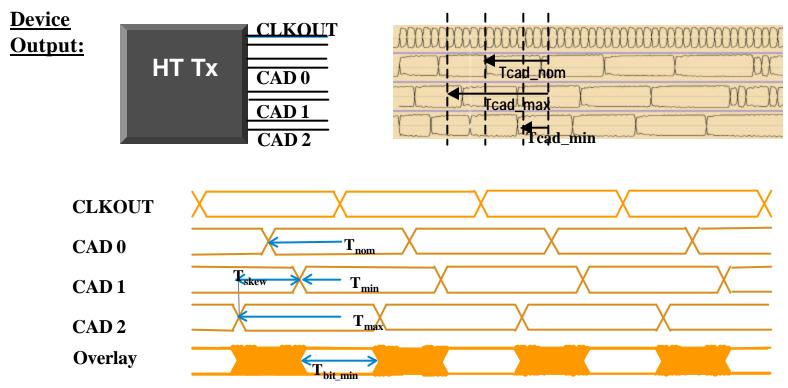

### **Application Example: North-Bridge Timing**

10 June, 2002 Testing High-Speed Interfaces

Agilent Restricted

**Agilent Technologies**

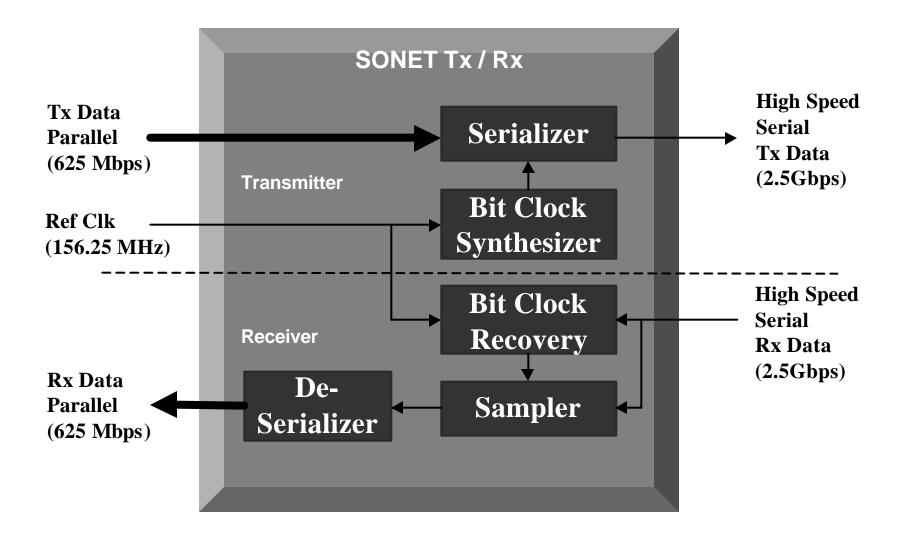

# Application Example: SONET Chip (OC48)

### **Test List for High-Speed Interfaces**

| TEST LIST                        | ATE NEEDS                                           |

|----------------------------------|-----------------------------------------------------|

| Impedance Test (Input, Output)   | DC Access                                           |

| Receiver Sensitivity Test        | Level Accuracy & Resolution<br>Low Swing capability |

| Receiver Skew Insertion          | Timing Accuracy & Resolution                        |

| Transmitter Skew Measurements    | Timing Accuracy, High Linearity                     |

| Dynamic Transmitter Voltage Test | Level Accuracy, High Bandwidth                      |

| Rise/Fall Time Measurements.     | High Bandwidth, High Resolution                     |

| Eye Mask Test                    | High Bandwidth, Voltage & Timing<br>Accuracy        |

| Jitter Test                      | Low System Jitter, All Others                       |

| Source Synchronous Test          | Source Synchronous Mode                             |

| HV Production Solution           | Full Integrated Solution,<br>High Throughput        |

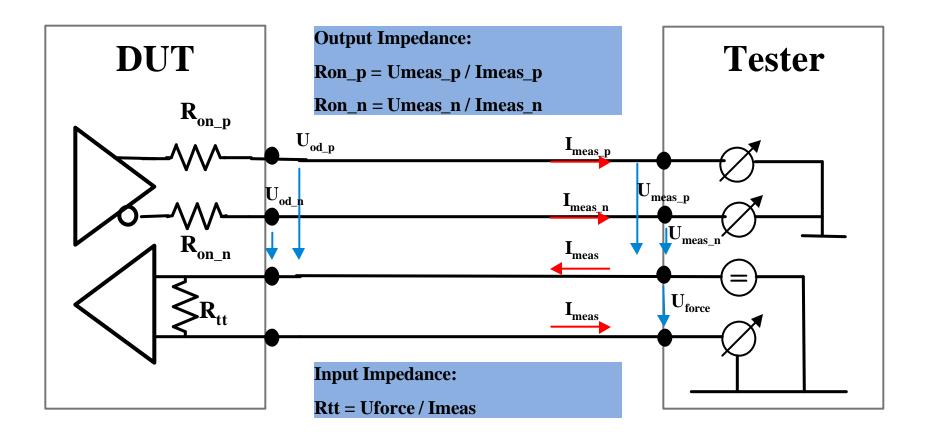

### **Impedance Test: Theory**

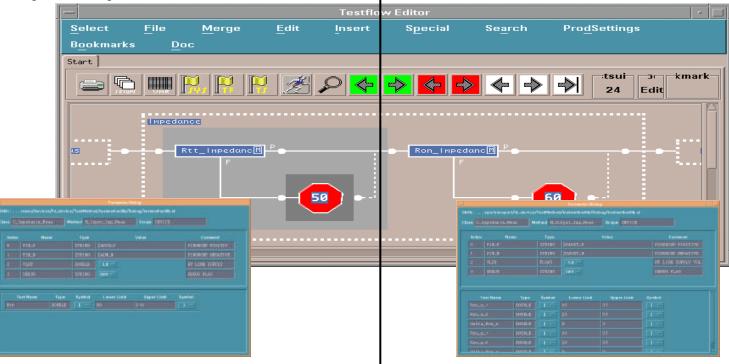

## Impedance Test: Tester Setup

Input Impedance

### • Output Impedance

- Pre-condition your device

- Force voltage: U<sub>force</sub>

- Current measurement: I<sub>meas</sub>

- Calculate Input Impedance: R=U<sub>force</sub>/I<sup>I</sup><sub>meas</sub>

- Pass/Fail decision

10 June, 2002 Testing High-Speed Interfaces Agilent Restricted

- Pre-condition your device

- DVM measurement: U<sub>meas</sub>

- Current measurement: I<sub>meas</sub>

- Calculate Input Impedance: R=U<sub>meas</sub>/I<sub>meas</sub>

- Pass/Fail decision

- Agilent Technologies

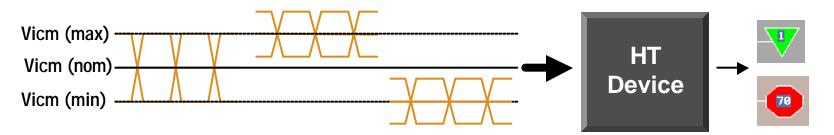

### At Speed Receiver Test: Sensitivity Test

#### **Input Sensitivity Test:**

- For RX functional test, different level sets can be used to run at the specified limits

- Requires only one functional pattern to test the part to its limits

.

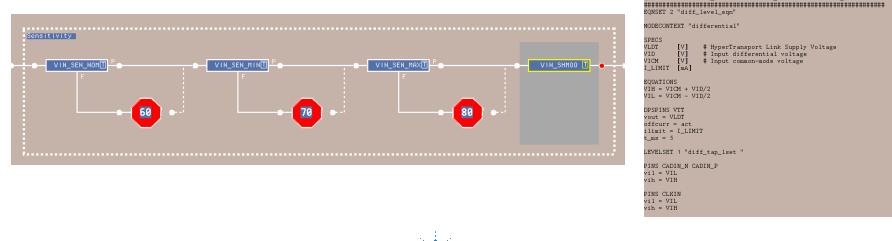

# Equation Set for Level Sensitivity Test: # Level Set 1:VLDT\_NOM = 1.20V VID\_NOM = 600mV VICM\_NOM = 600mV # Level Set 2:VLDT\_MIN = 1.14V VID\_MIN = 200mV VICM\_MIN = 440mV # Level Set 3:VLDT\_MAX = 1.26V VID\_MAX = 1000mV VICM\_MAX = 780mW

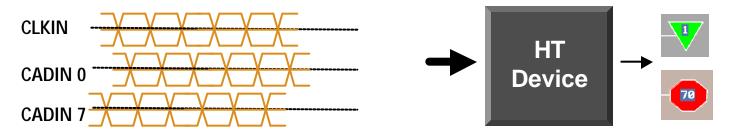

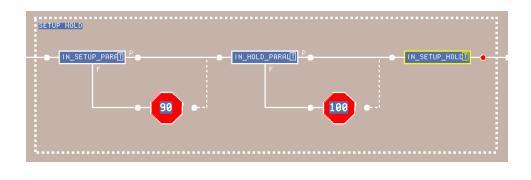

### **At Speed Receiver Test: Skew Insertion**

#### **Input InterSkew Test:**

- Program skew for all pins independently with spec variable

- Requires only one functional pattern to test the part to its limits

#### **Tester Setup:**

| - Test Control ·                                                                                                   |                                                                  |                                                                      |  |  |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------|--|--|

| Edit Doc                                                                                                           |                                                                  |                                                                      |  |  |

| Functional Test<br>Parametric                                                                                      |                                                                  |                                                                      |  |  |

| [run to]<br>[mask before]<br>[mask after]<br>[result pins]                                                         | vector<br>cycle<br>cycle<br>parallel                             | out_pins                                                             |  |  |

| [spec name]<br>[setup pins]<br>[method]<br>[start]<br>[stop]<br>[step]<br>[resolution]<br>[pass min]<br>[pass max] | timing<br>parallel<br>serial<br>ns<br>ps<br>ps<br>ps<br>ps<br>ps | t_setup_off<br>CADIN<br>0<br>#(@Tbit%T/2)<br>#20<br>0.01<br>0<br>116 |  |  |

| output PFunct (\$P)                                                                                                |                                                                  |                                                                      |  |  |

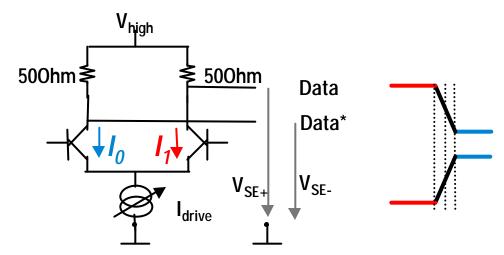

### **NP-Model Native Differential Driver**

### **Differential Driver: Current Switch**

**Retiming Unit**:

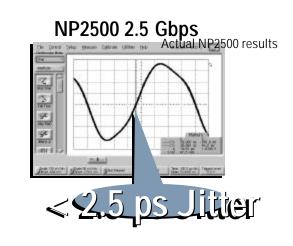

### PRBS: 2.5 Gbps, 50 mV Swing

**Agilent Technologies**

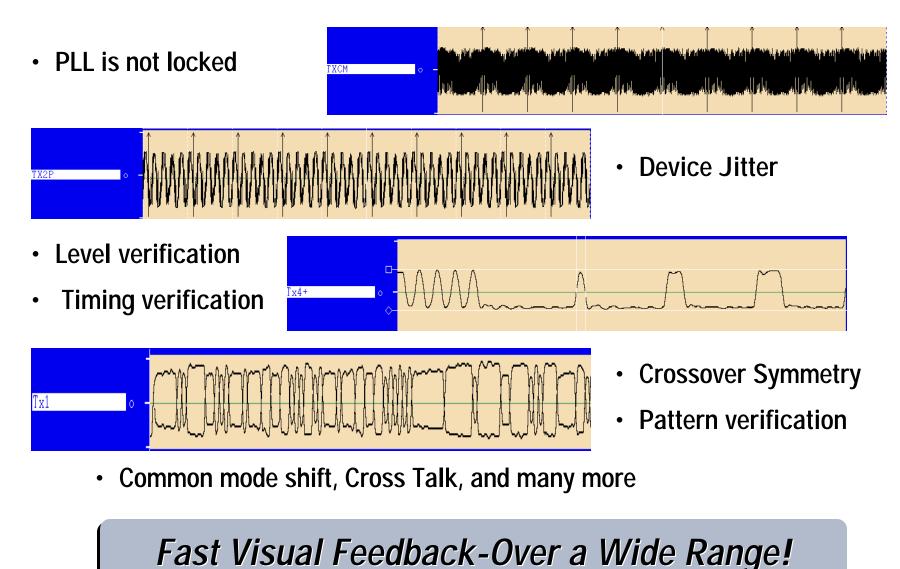

# Fast Debug with Timing Diagram

10 June, 2002 Testing High-Speed Interfaces Agilent Restricted

Agilent Technologies

## **Clock-Data Output Skew: Theory**

•T<sub>nom</sub>= Nominal setup time between Clock and Data/Control

- • $T_{min}$ = Minimal setup time

- •T<sub>max</sub>= Maximal setup time

- $T_{skew}$  = Maximal skew between data line  $T_{max}$   $T_{min}$

### At Speed Transmitter Test: Functional

•Search the clock edge (Tclk) and

•Program relative to the Tclk the edge delays

- •Tvalid = Tbit 2\*Tcad\_min

- •Apply a large pattern to guaranty worst-case output skew.

Agilent Restricted

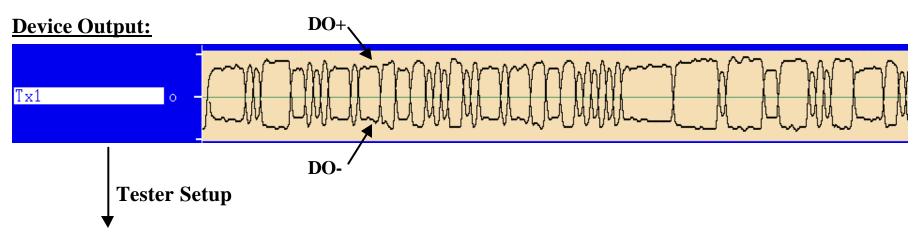

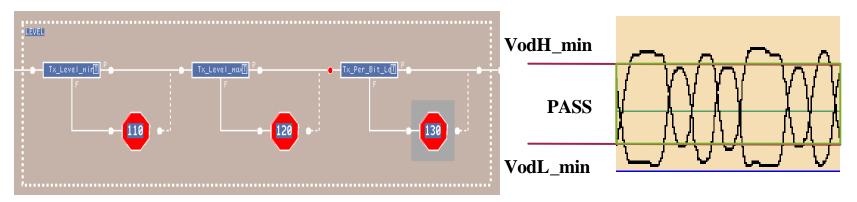

# At Speed Transmitter Test: Voltage

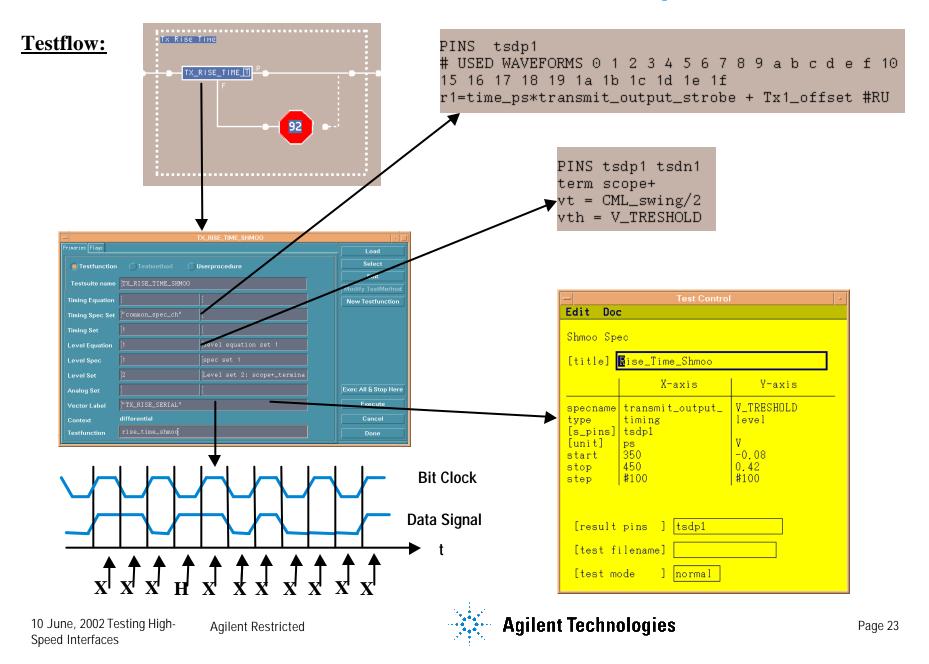

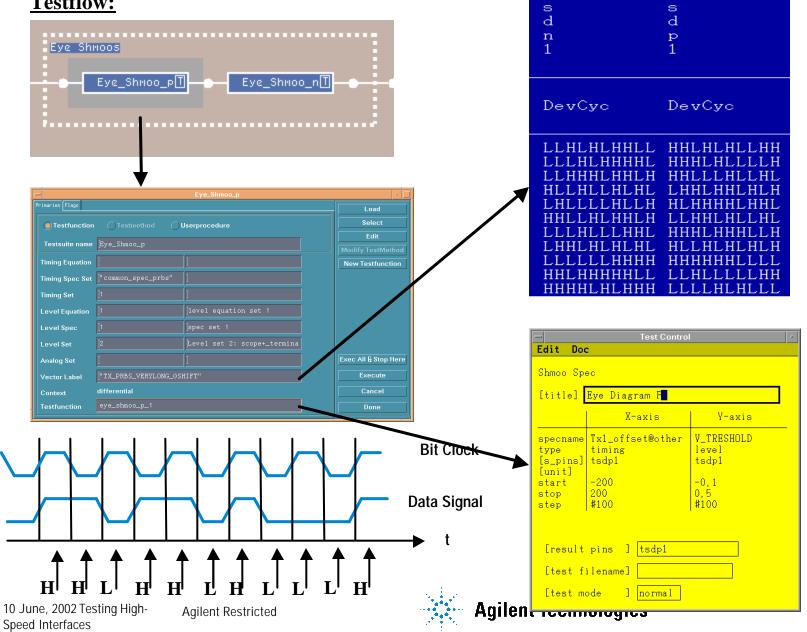

#### **Testflow:**

#### Minimum Output Voltage:

•Measure over a large number of samples to measure worstcase output voltage.

### Per Bit Voltage Measurement

### Summary

| ATE NEEDS                                           | COVERED                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC Access                                           | $\checkmark$                                                                                                                                                                                                                                                                                                                                                   |

| Level Accuracy & Resolution<br>Low Swing capability | ✓                                                                                                                                                                                                                                                                                                                                                              |

| Timing Accuracy & Resolution                        | $\checkmark$                                                                                                                                                                                                                                                                                                                                                   |

| Timing Accuracy, High Linearity                     | $\checkmark$                                                                                                                                                                                                                                                                                                                                                   |

| Level Accuracy, High Bandwidth                      | $\checkmark$                                                                                                                                                                                                                                                                                                                                                   |

| High Bandwidth, Resolution, Low<br>Overdrive        |                                                                                                                                                                                                                                                                                                                                                                |

| High Bandwidth, Voltage & Timing<br>Accuracy        |                                                                                                                                                                                                                                                                                                                                                                |

| Low System Jitter, All Others                       |                                                                                                                                                                                                                                                                                                                                                                |

| Source Synchronous Mode                             |                                                                                                                                                                                                                                                                                                                                                                |

| Full Integrated Solution,<br>High Throughput        | ×                                                                                                                                                                                                                                                                                                                                                              |

|                                                     | DC Access<br>Level Accuracy & Resolution<br>Low Swing capability<br>Timing Accuracy & Resolution<br>Timing Accuracy, High Linearity<br>Level Accuracy, High Bandwidth<br>High Bandwidth, Resolution, Low<br>Overdrive<br>High Bandwidth, Voltage & Timing<br>Accuracy<br>Low System Jitter, All Others<br>Source Synchronous Mode<br>Full Integrated Solution, |

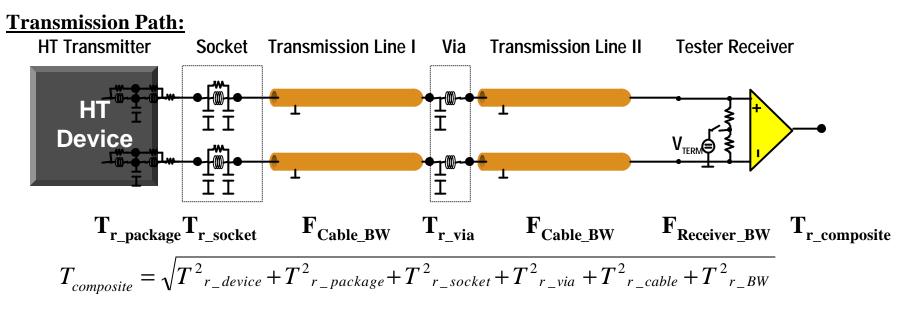

### **Rise/Fall Time Measurements: Theory**

#### **<u>DUT\_Board considerations:</u>**

- Uniform trace impedance across the whole trace (reflections)

- · Vias and other potential impedance discontinuities should be minimized (reflections)

- Make your trace width as wide as possible (skin effect)

- Talk to your PCB manufacturer about modeling techniques used

#### More Details:

- Hall, Hall, McCall: "High-Speed Digital System Design"

- Johnson, Graham: "High-Speed Digital Design"

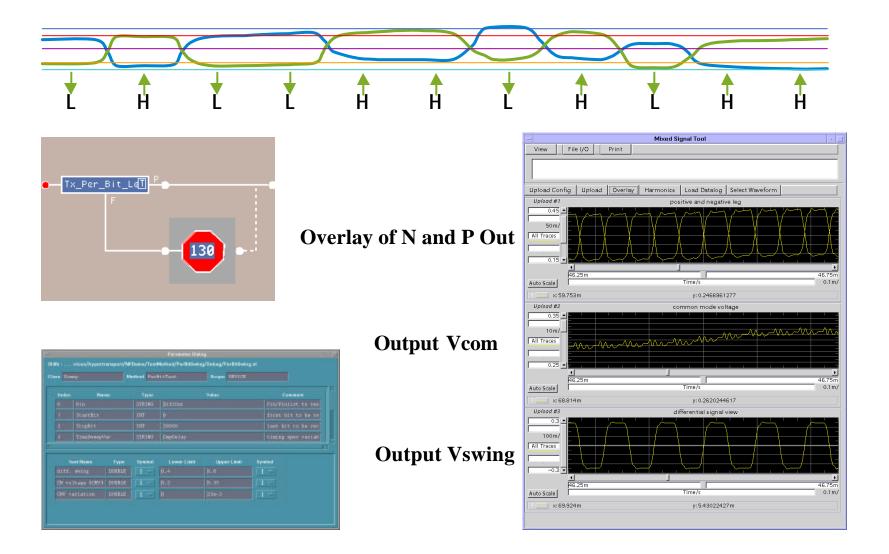

### **Rise/Fall Time Measurements: Setup**

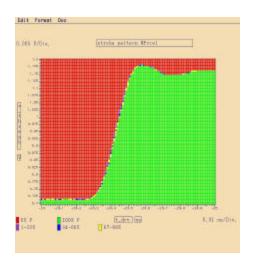

### **Rise/Fall Time Measurements: Results**

120 ps Rise Time @400 mV Swing @ the Receiver!

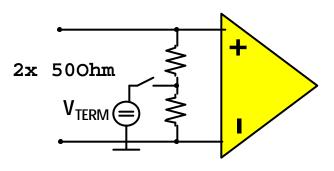

### **Differential Comparator**

### The Receiver matches the Application

- True differential

- Floating (and center tap) termination

- Outstanding bandwidth

- Built-in scope capability up to 2.5 Gbps

### Debug and Test the REAL DUT output!

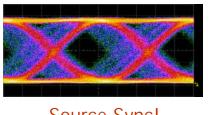

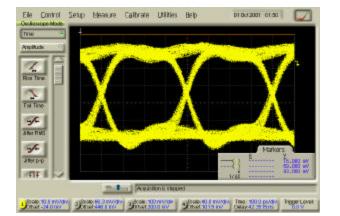

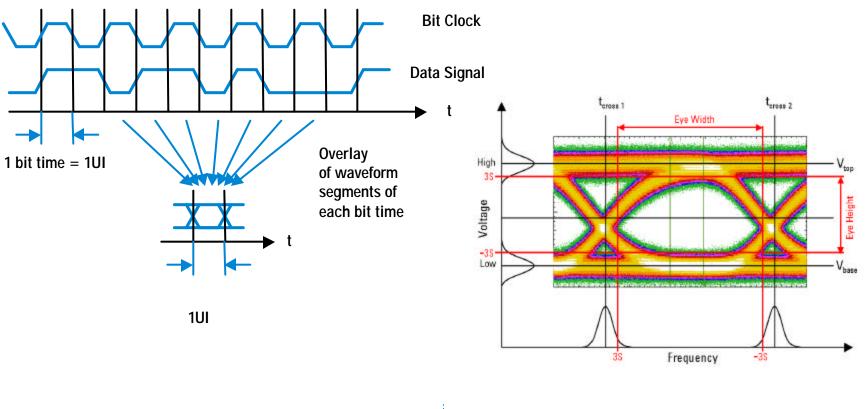

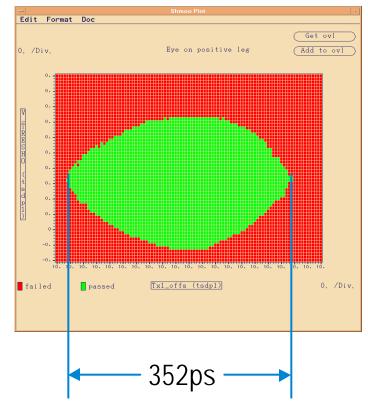

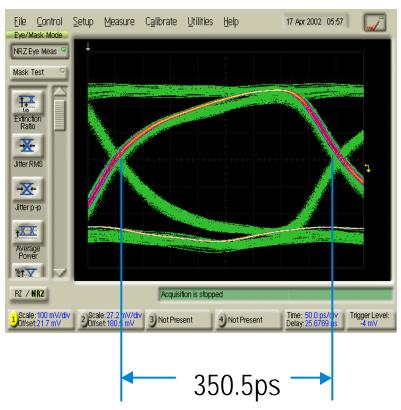

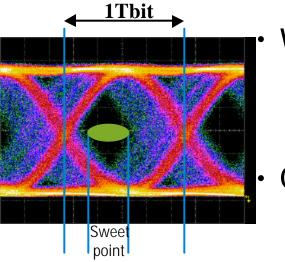

## **Eye Diagram: Theory**

**Eye diagram** is an overlay of many waveforms recorded with a bit clock as a trigger. This is a important parametric characteristics of the high speed transmit interface. Rise time/Fall time, jitter, and signal levels, overshoot, undershoot, ripple can be extracted from an eye diagram.

### **Eye Diagram: Setup**

#### **Testflow:**

Page 26

### Eye Diagram: Results I

### <u>Real Device Out @ 2.5 Gbps:</u> <u>Eye Shmoo:</u>

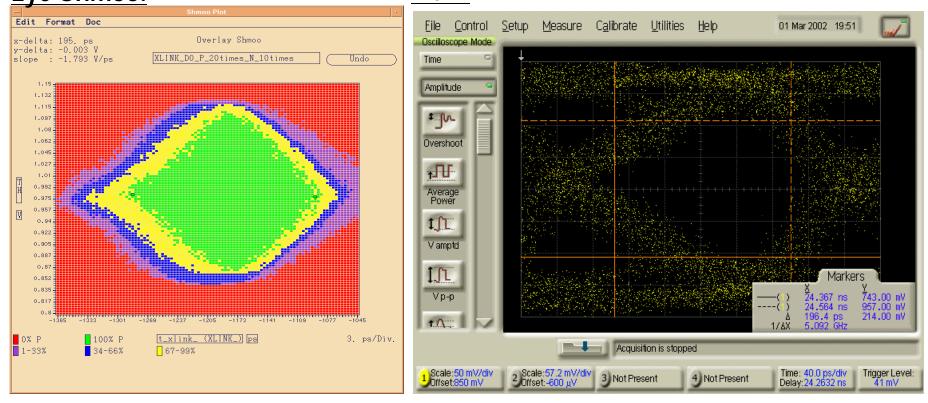

# Eye Diagram: Results II

### <u>Real Device Out @ 3.125 Gbps:</u> Eye Shmoo:

DCA:

# Speed Interfaces Agilent Restricted Agilent Restricted Agilent Technologies Page 28

### **Jitter Measurements**

1)Apply PRBS Pattern

Pin/ Group Names

P 0

r 1

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

t 0

2)Measurements & Calculation

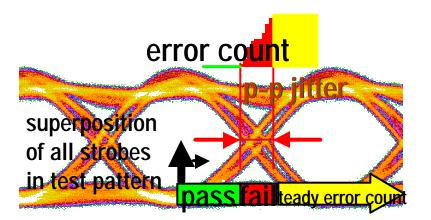

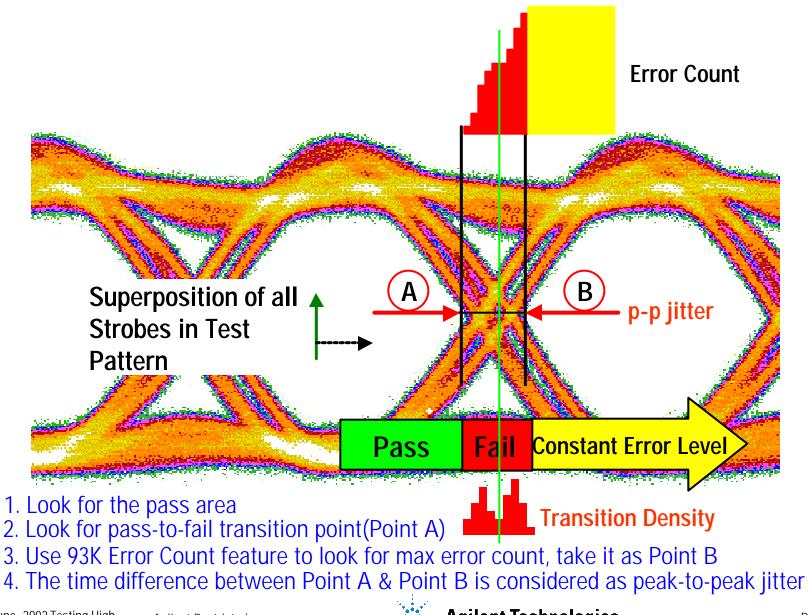

•Jitter Test at full speed on a PRBS Pattern

•Returns PP & RMS Value, etc.

•Real-time compare without capture & upload

•No additional instrument needed

10 June, 2002 Testing High-Speed Interfaces

Agilent Restricted

3) Histogram

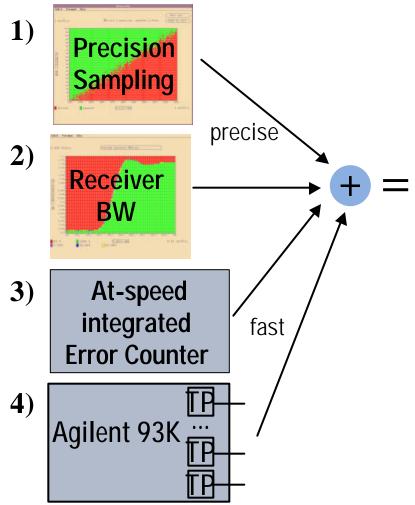

### **Ultra Fast Jitter Measurements**

Highly linear timing delay circuits per pin (5ps)

Resolution down to 1 ps

Superior comparator bandwidth

Test Processor-Per-Pin Architecture for PARALLEL execution

Error Counter

### **Jitter Measurement: Theory**

10 June, 2002 Testing High-Speed Interfaces

**Agilent Technologies**

### Implementation

|                 |                                              | <u>Z</u> 2 🔄                                    |                                                                | Testsuites<br>3 |

|-----------------|----------------------------------------------|-------------------------------------------------|----------------------------------------------------------------|-----------------|

| STA             | nHb: 1<br>ave: 6.203Hs<br>R T noadjust_funcT | nнb: 1<br>ave: 817.630нs<br>SyncTxMeasJitU<br>F | P<br>func_after<br>F                                           |                 |

|                 |                                              | SyncTxMeasJitter                                |                                                                |                 |

| Primaries Flags |                                              | Userprocedure                                   | <u>Input for Userproc.</u><br>(examples only):<br>0 = min. pin | d B2 ····       |

| Testsuite name  | [SyncTxMeasJitter                            |                                                 | 63 = max. pin                                                  | t               |

| Userproc name   | ∑SyncTx 0 63 4 3 -16                         | 40 0.2                                          | 4 = bit time - period (ns)                                     | htMethod        |

| Timing Equation | <u></u> 1                                    | Įstandard                                       | 3 = min_open_eye (ns)                                          |                 |

| Timing Spec Set |                                              | Ž250 Mbps                                       | -16 = start offset (ns)<br>40 = stop offset (ns)               |                 |

| Timing Set      | <u>1</u>                                     | [standard                                       | 0.2 = pass_max_jitter (ns)                                     |                 |

| Level Equation  | <u>)</u> 1                                   | [standard                                       |                                                                |                 |

| Level Spec      | <u>1</u>                                     | [3V                                             |                                                                | Stop Here       |

| Level Set       | <u>)</u> 1                                   | įsingle threshol                                |                                                                | ute             |

| Analog Set      |                                              | ¥.                                              |                                                                | cel             |

| Vector Label    | ∭ jitter_pattern"                            |                                                 |                                                                |                 |

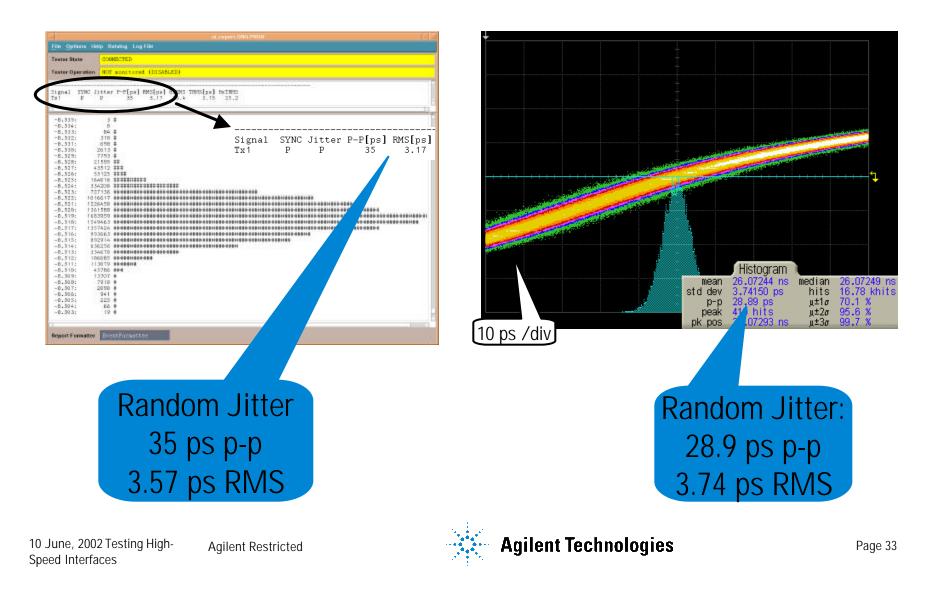

### Measurement Results: SerDes Device with Clock Signal

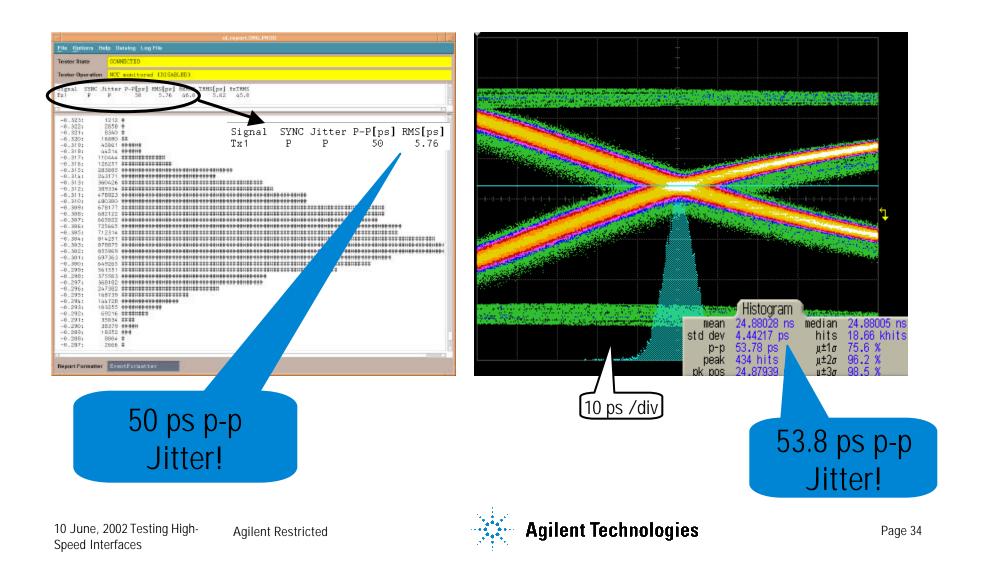

### Measurement Results: SerDes Device with Data Pattern (DDJ + RJ)

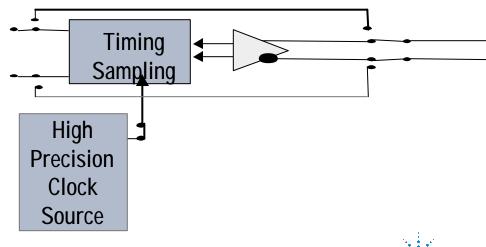

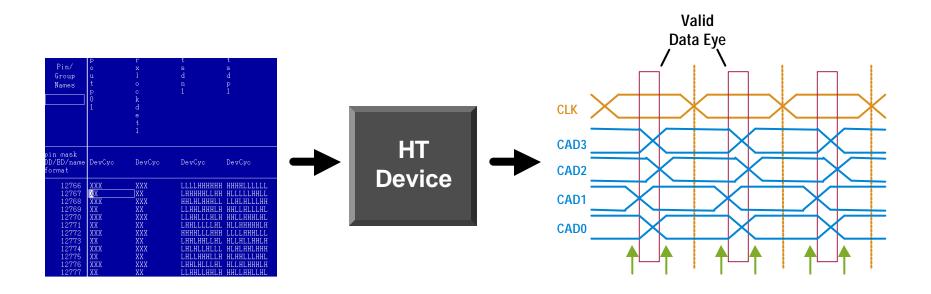

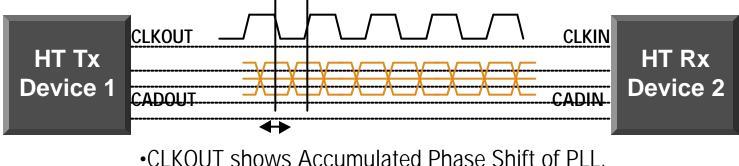

### The Source Synchronous Test Challenge

•CLKOUT shows Accumulated Phase Shift of Pl

•CADOUT moves with phase shift.

- What does the HT receiver see?

- Sampling Clock moves with shift

- Data eye stays open

- What does a "standard" ATE see?

- Sampling Clock is fixed

10 June 20 Data new closes lent Restricted Speed Interfaces

Agilent Technologies

### None Source Synchronous Tester

What is the minimum EPA a tester needs?

$$t_{\pm EPA} \leq \frac{\Delta t_{Bit} - \Delta t_{CumPhasErr} - \Delta t_{ProcessMargin}}{4}$$

Calculation example with: 1) 1UI = 800 Mbit Tbit = 1.25 ns 2) 1UI = 1.6 Gbit Tbit = 625 ps & Cum Phase Error = +/-250ps & Process Variation = +/- 50ps

1)

$$t_{\pm EPA\_800 \, Mbit} \le \frac{1.25 n s - 500 \, p s - 100 \, p s}{4} = 162.5 \, p s$$

2)

$$t_{\pm EPA\_1.6Gbit} \le \frac{625\,ps - 500\,ps - 100\,ps}{4} = 6.25\,ps$$

### **Conclusion:**

Beyond the Gigabit you will need a tester which operates Source Synchronous

## Summary

| ATE NEEDS                                           | COVERED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC Access                                           | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Level Accuracy & Resolution<br>Low Swing capability | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Timing Accuracy & Resolution                        | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Timing Accuracy, High Linearity                     | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Level Accuracy, High Bandwidth                      | <ul> <li>Image: A second s</li></ul> |

| High Bandwidth, Resolution, Low<br>Overdrive        | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| High Bandwidth, Voltage & Timing<br>Accuracy        | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Low System Jitter, All Others                       | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Source Synchronous Mode                             | $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Full Integrated Solution,<br>High Throughput        | ✓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                     | DC Access<br>Level Accuracy & Resolution<br>Low Swing capability<br>Timing Accuracy & Resolution<br>Timing Accuracy, High Linearity<br>Level Accuracy, High Bandwidth<br>High Bandwidth, Resolution, Low<br>Overdrive<br>High Bandwidth, Voltage & Timing<br>Accuracy<br>Low System Jitter, All Others<br>Source Synchronous Mode<br>Full Integrated Solution,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |